[뉴스토마토 오세은 기자]

삼성전자(005930)가 최근 조직개편을 통해 ‘첨단패키징팀’을 신설했다. 차세대 패키징 기술로 한계에 다다르고 있는 반도체 미세화 공정 한계를 뛰어넘겠다는 의지로 해석된다.

14일 외신과 업계 등에 따르면 지난 주 조직개편을 단행한 삼성전자는 DS(반도체)부문 TSP(테스트&시스템 패키지) 사업부 산하에 첨단패키징팀을 새롭게 꾸렸다. 패키징은 전 공정을 끝낸 웨이퍼(반도체 원재료)를 반도체 모양으로 자르거나 배선을 연결하는 작업으로 업계에서는 ‘후공정’이라고도 부른다.

삼성전자의 첨단패키징팀 신설은 반도체가 다기능, 고성능화하면서 기존 기술로는 구현 못하는 공정 미세화를 패키징 기술로 돌파하겠다는 전략으로 풀이된다. 실제 삼성전자가 지난 11월 개발에 성공한 차세대 그래픽 D램인 GDDR6W도 차세대 패키지 기술인 팬 아웃 웨이퍼 레벨 패키지(Fan-Out Wafer level Package)가 적용되면서 용량과 성능이 2배 향상됐다.

과거 반도체 패키징은 반도체를 포장해 칩을 보호하는 역할에 그쳤지만, 4차 산업혁명으로 인한 인공지능(AI), 사물인터넷(IoT)을 탑재한 제품 내 반도체들이 고성능과 저전력을 요하면서 기존 미세공정으로는 연산 처리 능력을 극대화하는 미세화 공정이 한계에 이르렀다. 반도체 기업들이 반도체 효율을 높이기 위해 차세대 패키징 기술이나 갈륨나이트라이드(GaN) 차세대 웨이퍼 등에 사활을 거는 이유다.

패키징은 4단계 공정으로 이뤄진다.

먼저 웨이퍼 위에 수백 개의 칩을 다이아몬드 톱이나 레이저광선을 이용해 낱개의 칩으로 분리하는 ‘웨이퍼 절단’ 과정이 실시된다. 절단된 칩들은 리드프레임(칩 지지대)나 PCB 기판 위에 올려진다. 다음 반도체의 전기적 특성을 위해 반도체 칩과 기판을 금속으로 연결하는 금속 연결 공정이 이뤄지고, 마지막으로 원하는 형태의 패키지로 만드는 성형(몰딩)이 진행된다.

삼성의 대표적인 차세대 패키징 기술 중 하나는 3차원 실리콘 관통전극(3D-TSV)이다.

TSV는 금속(와이어)을 이용해 칩을 연결하는 대신 반도체 칩 상단과 하단에 마이크로미터 직경(머리카락 굵기의 20분의 1 수준)의 전자 이동통로(TSV) 수만 개를 만들어 오차 없이 연결하는 패키징 기술이다. 기존 와이어 본딩 보다 신호를 주고받는 시간을 줄여 속도와 소비전력을 개선시킬 수 있다.

업계 관계자는 “반도체의 효율을 높이는 방법은 차세대 패키징 기술, GaN웨이퍼 등을 적용하는 방법이 있다”며 “반도체 업체들이 여러 시도를 통해 미세화 공정 한계 돌파에 나서고 있다”고 말했다.

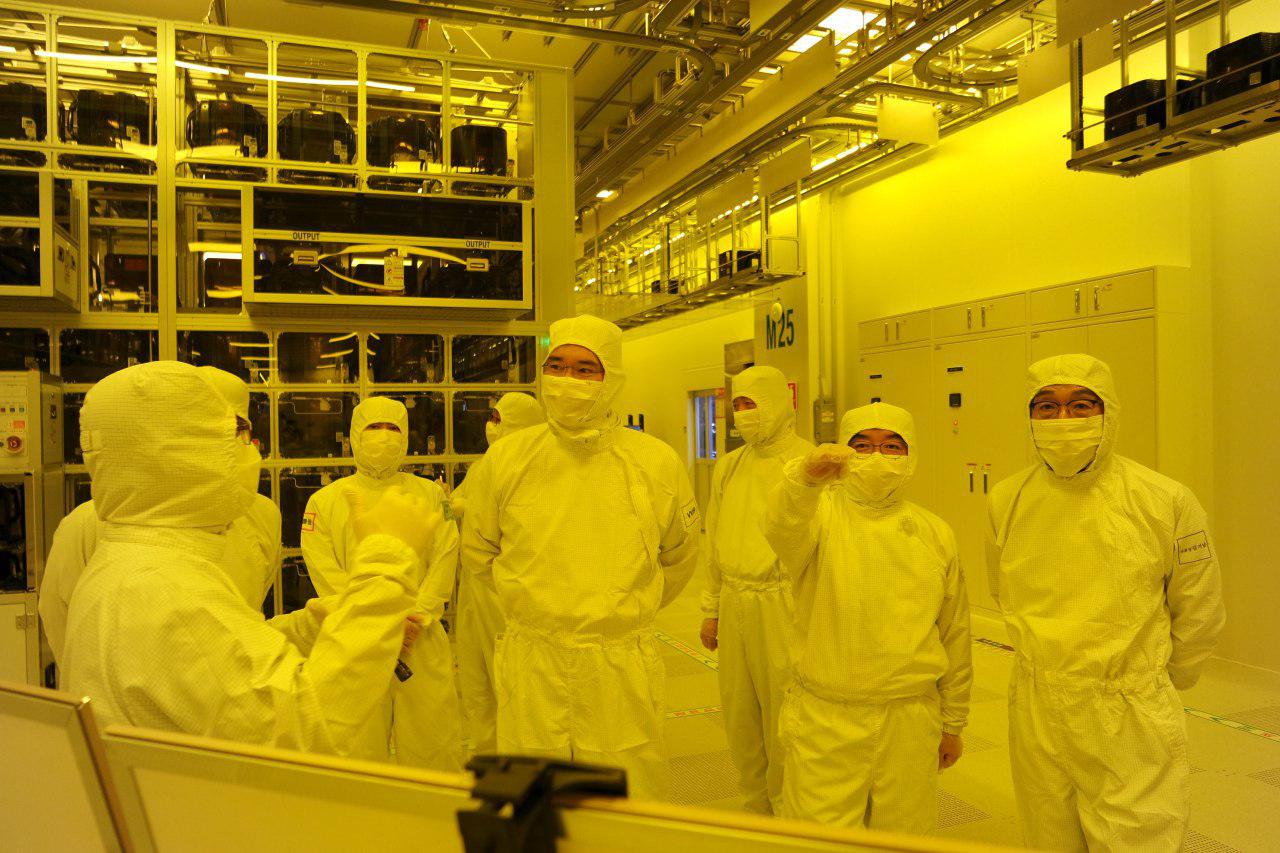

2019년 8월 이재용 삼성전자 회장(가운데)이 패키징 공정이 이뤄지는 충남 아산 소재 온양캠퍼스를 찾아 반도체 패키징 라인을 둘러보고 있다. (사진=삼성전자)

오세은 기자 ose@etomato.com